# SO6103 Digital Proximity Sensor

### 1. Features

- Proximity Detection with an Integrated LED Driver

- Proximity Detection

- Programmable Offset Control Register

- Programmable Analog Gain and Integration Time

- Current Sink Driver for External IR LED

- Power Management

- Low Power 1uA Sleep State

- 70uA Wait State with Programmable Wait Time from 3ms to 10seconds

- I2C Interface Compatible

- Up to 400kHz (I2C Fast Mode)

- Device addr. : 0x39 (7bit)

# 2. Applications

- Cell Phone Touch Screen Disable

- Mechanical Switch Replacement

- Automatic Speakerphone Enable

- Automatic Menu Popup

# 3. Description

The proximity detection feature allows a large dynamic range of operation for use in short distance detection behind dark glass such as in a cell phone or for longer distance measurements for applications such as presence detection for monitors or laptops. The programmable proximity detection enables continuous measurements across the entire range. In addition, an internal state machine provides the ability to put the device into a low power mode measurements providing very low average power consumption.

# **Table of Contents**

| 1 | Features                        | 1 | 7 | Application  | 21 |

|---|---------------------------------|---|---|--------------|----|

| 2 | Applications                    | 1 | 8 | IC Dimension | 22 |

| 3 | Description                     | 1 |   |              |    |

| 4 | Pin Configuration and Functions | 3 |   |              |    |

| 5 | Specifications                  | 4 |   |              |    |

| 6 | Detailed Description            | 7 |   |              |    |

|   |                                 |   |   |              |    |

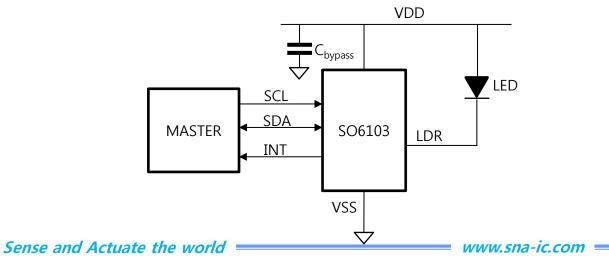

# 4. Pin Configuration and Functions

### **Pin Functions**

| PIN | I/O/P/G | DESCRIPTION                                     |  |  |  |

|-----|---------|-------------------------------------------------|--|--|--|

| LDR | 0       | Proximity IR LED controlled current sink driver |  |  |  |

| SCL | Ι       | 2C serial clock input terminal                  |  |  |  |

| SDA | I/O     | I2C serial data input/output terminal           |  |  |  |

| VDD | Р       | Supply voltage                                  |  |  |  |

| INT | 0       | Interrupt – open drain (active low)             |  |  |  |

| VSS | G       | Supply Ground                                   |  |  |  |

# 5. Specifications

### 5.1 Absolute Maximum Ratings

| SYMBOL | PARAMETER              | MIN  | MAX  | UNIT |

|--------|------------------------|------|------|------|

| VDD    | Power Supply Voltage   | -0.3 | 6    | V    |

| Vin    | Input Voltage          | -0.3 | VDD  | V    |

| Vout   | Output Voltage         | -0.3 | VDD  | V    |

| Vhbm   | Static Discharge (HBM) |      | 2000 | V    |

| Vmm    | Static Discharge (MM)  |      | 200  | V    |

| Tj     | Junction Temperature   | -40  | 125  | °C   |

+ Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Note 1: All voltage values are with respect to VSS.

### 5.2 Recommended Operating Conditions

| SYMBOL | PARAMETER                     | MIN | ТҮР | MAX | UNIT |

|--------|-------------------------------|-----|-----|-----|------|

| VDD    | Power Supply Voltage          | 2.7 | 3.0 | 5   | V    |

| Vin    | Input Voltage                 | 0   |     | VDD | V    |

| Vout   | Output Voltage                | 0   |     | VDD | V    |

| TA     | Operating ambient temperature | -40 |     | 85  | °C   |

*— Sense and Actuate the world*

# 5.3 Electrical Characteristics (VDD = 3V, Ta = 25°C)

| PARAMETER                      | TEST CONDITIONS                      | MIN    | ТҮР | MAX        | UNIT |

|--------------------------------|--------------------------------------|--------|-----|------------|------|

|                                | Active – LDR pulses off              |        | 158 |            |      |

| Supply Current                 | Wait state                           |        | 55  |            | uA   |

|                                | Sleep state                          |        | 1   | 10         |      |

| INT, SDA output<br>low voltage | 3mA sink current<br>6mA sink current | 0<br>0 |     | 0.4<br>0.6 | V    |

| Low Level Input<br>Voltage     |                                      |        |     | 0.3VDD     | V    |

| High Level Input<br>Voltage    |                                      | 0.7VDD |     |            | V    |

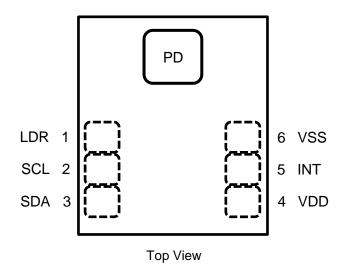

### 5.4 Data Transmission Timing Requirements

| PARAMETER                                    | Symbol              | CONDITIONS | MIN | MAX | UNIT |

|----------------------------------------------|---------------------|------------|-----|-----|------|

| Output Low Level (SDA)                       | V <sub>OL</sub>     | IOL = 4mA  |     | 0.5 | V    |

| SCLK Operating Frequency                     | f <sub>SCLK</sub>   |            |     | 400 | kHz  |

| Stop and Start Condition                     | t <sub>BUF</sub>    |            | 1.3 |     | us   |

| Hold Time After Repeated Start<br>Conditions | t <sub>HD;STA</sub> |            | 0.6 |     | us   |

| SCLK Clock Low Period                        | t <sub>LOW</sub>    |            | 1.3 |     | us   |

| SCLK Clock High Period                       | t <sub>HIGH</sub>   |            | 0.6 |     | us   |

| Repeated Start Condition Setup<br>Time       | t <sub>su;sta</sub> |            | 0.6 |     | us   |

| Data Hold Time                               | t <sub>HD;DAT</sub> |            | 0   | 0.9 | us   |

| Data Setup Time                              | t <sub>SU;DAT</sub> |            | 100 |     | ns   |

| Clock/Data Fall Time                         | t <sub>F</sub>      |            |     | 300 | ns   |

| Clock/Data Rise Time                         | t <sub>R</sub>      |            |     | 300 | ns   |

| Stop Condition Setup Time                    | t <sub>su;sto</sub> |            | 0.6 |     | us   |

= Sense and Actuate the world =

# 5.5 Proximity Characteristics (VDD = 3V, Ta = $25^{\circ}C$ , PEN = 1)

| PARAMETER              | TEST CONDITIONS |                                                      | MIN | ТҮР                    | MAX   | UNIT   |

|------------------------|-----------------|------------------------------------------------------|-----|------------------------|-------|--------|

| Prox. Full count value |                 |                                                      |     |                        | 65535 | counts |

|                        | PDL = 0         | PDRIVE = 0<br>PDRIVE = 1<br>PDRIVE = 2<br>PDRIVE = 3 |     | 125<br>100<br>75<br>50 |       | mA     |

| LED drive current      | PDL = 1         | PDRIVE = 0<br>PDRIVE = 1<br>PDRIVE = 2<br>PDRIVE = 3 |     | 12.5<br>10<br>7.5<br>5 |       | mA     |

| Prox. offset           | PC              | DRIVE = 0                                            |     |                        | 4     | counts |

### 6. Detailed Description

### 6.1 Overview

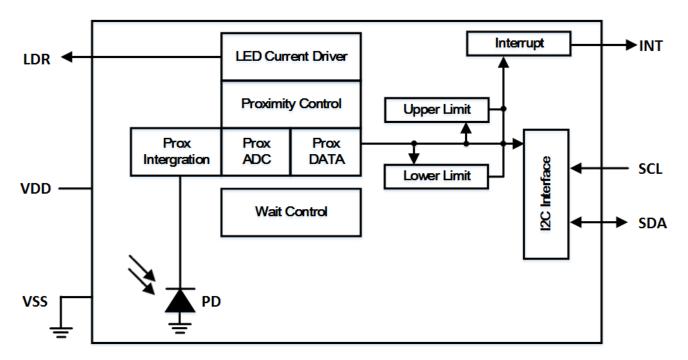

The SO6103 device provides on-chip photo diode, integrating amplifier, ADC, accumulator, clock, buffer, comparator, a state machine and an I2C interface. Integrating ADC simultaneously convert the amplified photodiode currents into a digital value providing up to 16 bits of resolution.

The device is standby I2C interface which supports up to 400-kbits/s data rate. The digital interface supports IO levels from 2.7V to 5.0V.

### 6.2 Function Block Diagram

### 6.3 Feature Description

### 6.3.1 System State machine

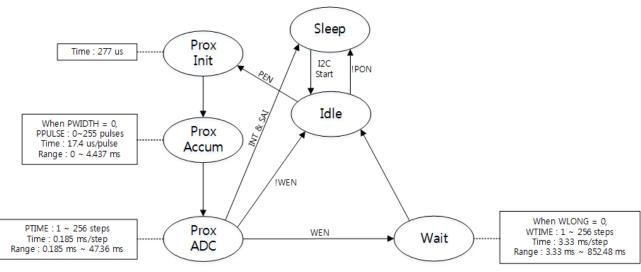

An internal state machine provides system control of the proximity detection, power management features of the device. At power up, an internal power-on-reset initializes the device and puts it in a low-power Sleep state.

When a start condition is detected on the I2C bus, the device transitions to the Idle state where it checks the Enable register (0x00) PON bit. If PON is disabled, the device will return to the Sleep state to save power. Otherwise, the device will remain in the Idle state until a proximity function is enabled. Once enabled, the device will execute the Prox., Wait states in sequence as indicated in Figure 1. Upon completion and return to Idle, the device will automatically begin a new prox.-wait cycle as long as PON and either PEN remain enabled.

PON, PEN, WEN and SAI are fields in the ENABLE register (0x00).

#### Figure 1. State Diagram

Sense and Actuate the world

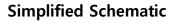

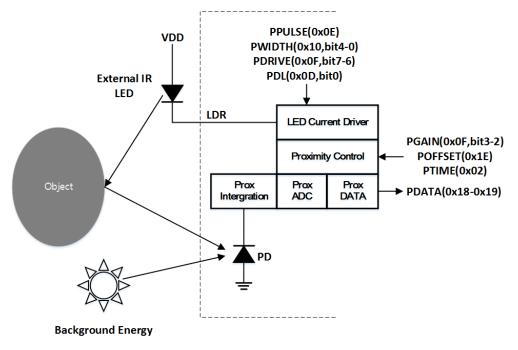

## 6.3.2 Proximity Detection

Proximity detection is accomplished by measuring the amount of light energy, generally from an IR LED, reflected off an object to determine its distance. The proximity light source, which is external to the SO6103 device, is driven by the integrated proximity LED current driver as shown in Figure 2.

Figure 2. Proximity Detection

The LED current driver, output on the LDR terminal, provides a regulated current sink that eliminates the need for an external current limiting resistor. The combination of proximity LED drive strength (PDRIVE) determine the drive current. PDRIVE sets the drive current to 125mA, 100mA, 75mA, or 50mA. To drive an external light source with more than 125 mA or to minimize on-chip ground bounce, LDR can be used to drive an external p-type transistor, which in turn drives the light source.

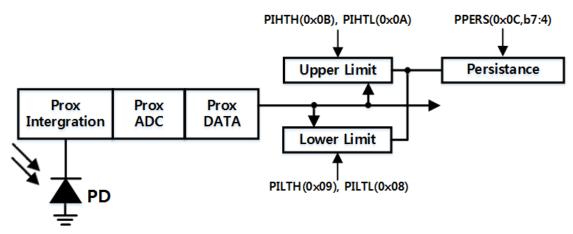

# 6.3.3 Interrupt

The interrupt feature simplifies and improves system efficiency by eliminating the need to poll the sensor for proximity values outside a user-defined range. While the interrupt function is always enabled and its status is available in the Status register (0x13), the output of the interrupt state can be enabled using the proximity interrupt enable (PIEN) field in the Enable register (0x00).

Two 16-bit interrupt threshold registers allow the user to set limits below and above a desired proximity range. An interrupt can be generated when the proximity data (PDATA) is less than the proximity interrupt low threshold (PILTx) or is greater than the proximity interrupt high threshold (PIHTx).

To further control when an interrupt occurs, the device provides an interrupt persistence feature. The persistence filter allows the user to specify the number of consecutive out-of-range proximity occurrences before an interrupt is generated. The persistence filter register (0x0C) allows the user to set the proximity persistence filter (PPERS) values. See the persistence filter register for details on the persistence filter values.

Figure 3. Programmable Interrupt

### 6.4 Programming

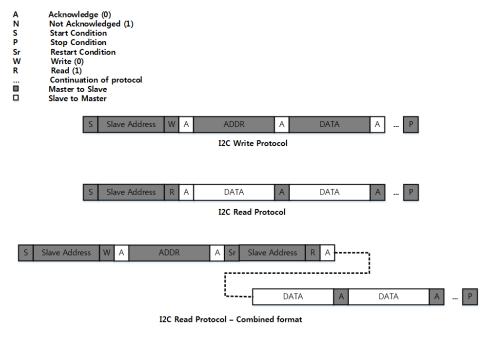

# 6.4.1 I2C Protocol

Interface and control of the SO6103 is accomplished through an I2C serial compatible interface (standard or fast mode) to a set of registers that provide access to device control functions and output data. The device supports a single slave address of 0x39 hex using 7-bit addressing protocol. (Contact factory for other addressing options.)

The I2C standard provides for three types of bus transaction: read, write, and a combined protocol (Figure 4). During a write operation, the first byte written is a command byte followed by data. In a combined protocol, the first byte written is the command byte followed by reading a series of bytes. If a read command is issued, the register address from the previous command will be used for data access. Likewise, if the MSB of the command is not set, the device will write a series of bytes at the address stored in the last valid command with a register address. The command byte contains either control information or a 5-bit register address. The control commands can also be used to clear interrupts.

For a complete description of I2C protocols, please review the I2C Specification at: http://www.semiconductors.philips.com.

< Figure 4. I2C Protocols>

*— Sense and Actuate the world*

# 6.5 Register Maps

| ADDRESS | NAME     | R/W | REGISTER FUNCTION                  | DEFAULT |

|---------|----------|-----|------------------------------------|---------|

| -       | COMMAND  | W   | Specifies register address         | 0x00    |

| 0x00    | ENABLE   | RW  | Enable states and interrupts       | 0x00    |

| 0x02    | PTIME    | RW  | Proximity time                     | 0xFF    |

| 0x03    | WTIME    | RW  | Wait time                          | 0xFF    |

| 0x08    | PILTL    | RW  | interrupt low threshold low byte   | 0x00    |

| 0x09    | PILTH    | RW  | interrupt low threshold high byte  | 0x00    |

| 0x0A    | PIHTL    | RW  | interrupt high threshold low byte  | 0x00    |

| 0x0B    | PIHTH    | RW  | interrupt high threshold high byte | 0x00    |

| 0x0C    | PERS     | RW  | Interrupt persistence filter       | 0x00    |

| 0x0D    | CONFIG   | RW  | Configuration                      | 0x00    |

| 0x0E    | PPCOUNT  | RW  | Pulse count                        | 0x00    |

| 0x0F    | CONTROL  | RW  | Control register                   | 0x00    |

| 0x10    | PWIDTH   | RW  | Pulse width                        | 0x00    |

| 0x12    | ID       | R   | Device ID                          | 0x03    |

| 0x13    | STATUS   | R   | Device status                      | 0x00    |

| 0x18    | PDATAL   | R   | Proximity data low byte            | 0x00    |

| 0x19    | PDATAH   | R   | Proximity data high byte           | 0x00    |

| 0xE5    | INTCLEAR | W   | Interrupt clear                    | 0x00    |

### 6.5.1 ADDR(COMMAND) Register

The ADDR (COMMAND) register specifies the address of the target register for future read and write operations, as well as issues special function commands.

|      | 7   | 6  | 5  | 4 | 3 | 2      | 1 | 0 |                 |

|------|-----|----|----|---|---|--------|---|---|-----------------|

| ADDR | SEL | ΤY | PE |   |   | ADDR/S | F |   | Default<br>0x00 |

| FIELD       | BITS | DESCRIPTI       | ION ( Default = 0x00 )                                                         |

|-------------|------|-----------------|--------------------------------------------------------------------------------|

|             |      | Select SF/ADDR  | R Register.                                                                    |

| SEL         | 7    | FIELD VALUE     | DESCRIPTION                                                                    |

| SEL         | /    | 0               | Address Select                                                                 |

|             |      | 1               | Special Function Select                                                        |

|             |      | Selects type of | transaction to follow in subsequent data transfers:                            |

|             | 6:5  | FIELD VALUE     | DESCRIPTION                                                                    |

| ТУЛГ        |      | 00              | Repeated byte protocol transaction                                             |

| TYPE        |      | 01              | Auto-increment protocol transaction                                            |

|             |      | 10              | Reserved — Do not use                                                          |

|             |      | 11              | Special function — See description below                                       |

|             |      |                 | pecial function field.<br>Isted below apply only to special function commands: |

| ADDR<br>/SF | 4:0  | FIELD VALUE     | DESCRIPTION                                                                    |

| , , , , ,   |      | 00101           | interrupt clear                                                                |

|             |      | other           | Reserved — Do not use                                                          |

#### 6.5.2 ENABLE Register (0x00)

|          | 7        | 6                                                                                                                                                                                | 5                                                                                                                           | 4        | 3                          | 2   | 1           | 0         |                 |  |  |  |

|----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------|----------------------------|-----|-------------|-----------|-----------------|--|--|--|

| ENABLE   | Reserved | SAI                                                                                                                                                                              | PIEN                                                                                                                        | Reserved | WEN                        | PEN | Reserved    | PON       | Default<br>0x00 |  |  |  |

| FIELD    | BITS     | DES                                                                                                                                                                              | DESCRIPTION ( Default = 0x00 )                                                                                              |          |                            |     |             |           |                 |  |  |  |

| Reserved | 7        | Reserved                                                                                                                                                                         | . Write as                                                                                                                  | 0.       |                            |     |             |           |                 |  |  |  |

| SAI      | 6        |                                                                                                                                                                                  | •                                                                                                                           |          | nsserted, th<br>upt has be |     | •           | down at t | the end of      |  |  |  |

| PIEN     | 5        | -                                                                                                                                                                                | Proximity interrupt Enable. When asserted permits proximity interrupts to be generated, subject to the persist filter.      |          |                            |     |             |           |                 |  |  |  |

| Reserved | 4        | Reserved                                                                                                                                                                         | . Write as                                                                                                                  | 0.       |                            |     |             |           |                 |  |  |  |

| WEN      | 3        |                                                                                                                                                                                  |                                                                                                                             |          | s the wait<br>e wait tim   |     | Vriting a 1 | activates | the wait        |  |  |  |

| PEN      | 2        | 1 2                                                                                                                                                                              | Proximity enable. This bit activates the proximity function. Writing a 1 enables proximity. Writing a 0 disables proximity. |          |                            |     |             |           |                 |  |  |  |

| Reserved | 1        | Reserved                                                                                                                                                                         | . Write as                                                                                                                  | 0.       |                            |     |             |           |                 |  |  |  |

| PON      | 0        | Power ON. This bit activates the internal oscillator to permit the timers and ADC channel to operate. Writing a 1 activates the oscillator. Writing a 0 disables the oscillator. |                                                                                                                             |          |                            |     |             |           |                 |  |  |  |

The enable register is used to power the device on/off, enable functions, and interrupts.

#### 6.5.3 PTIME Register (0x02)

The proximity time register controls the integration time of the proximity ADC in 0.185 ms increments. Upon power up, the proximity time register is set to 0xFF. It is recommended that this register be programmed to a value of 0xFF (1 integration cycle).

| FIELD | BITS | DESCRIPTION ( Default = 0xFF ) |              |          |  |  |  |

|-------|------|--------------------------------|--------------|----------|--|--|--|

|       |      | VALUE                          | INTEG_CYCLES | TIME     |  |  |  |

|       |      | 0xFF                           | 1            | 0.185 ms |  |  |  |

| PTIME | 7:0  | 0xFE                           | 2            | 0.390 ms |  |  |  |

|       |      |                                |              |          |  |  |  |

|       |      | 0x00                           | 256          | 47.36 ms |  |  |  |

#### 6.5.4 WTIME Register (0x03)

Wait time is set 3.33 ms increments unless the WLONG bit is asserted in which case the wait times are  $12 \times 100$  power. WTIME is programmed as a 2's complement number. Upon power up, the wait time register is set to 0xFF.

| FIELD | BITS | DESCRIPTION ( Default = 0xFF ) |           |               |               |  |  |  |  |

|-------|------|--------------------------------|-----------|---------------|---------------|--|--|--|--|

|       |      | VALUE                          | WAIT TIME | TIME(WLONG=0) | TIME(WLONG=1) |  |  |  |  |

|       |      | 0xFF                           | 1         | 3.33 ms       | 0.04 sec      |  |  |  |  |

| WTIME | 7:0  | 0xFE                           | 2         | 6.66 ms       | 0.08 sec      |  |  |  |  |

|       |      |                                |           |               |               |  |  |  |  |

|       |      | 0x00                           | 256       | 852.48 ms     | 10.2 sec      |  |  |  |  |

#### 6.5.5 Proximity Interrupt Threshold Registers (0x08 - 0x0B)

The proximity interrupt threshold registers provide the upper and lower threshold values to the proximity interrupt comparators. See Interrupts in the Principles of Operation section for detailed information. Upon power up, the interrupt threshold registers reset to 0x00.

| REGISTER | ADDRESS | BITS | DESCRIPTION                                  |  |

|----------|---------|------|----------------------------------------------|--|

| PILTL    | 0x08    | 7:0  | Proximity interrupt low threshold low byte   |  |

| PILTH    | 0x09    | 7:0  | Proximity interrupt low threshold high byte  |  |

| PIHTL    | 0x0A    | 7:0  | Proximity interrupt high threshold low byte  |  |

| PIHTH    | 0x0B    | 7:0  | Proximity interrupt high threshold high byte |  |

### 6.5.6 Interrupt Persistence Filter Register (0x0C)

The interrupt persistence filter sets the number of consecutive proximity cycles that are outof-range before an interrupt is generated. Out-of-range is determined by the proximity interrupt threshold registers (0x08 through 0x0B). See Interrupts in the Principles of Operation section for further information. Upon power up, the interrupt persistence filter register resets to 0x00, which will generate an interrupt at the end of each proximity cycle.

|      | 7 | 6   | 5   | 4 | 3 | 2    | 1    | 0 |                 |

|------|---|-----|-----|---|---|------|------|---|-----------------|

| PERS |   | PPI | ERS |   |   | Rese | rved |   | Default<br>0x00 |

| FIELD    | BITS | DESCRIPTION ( Default = 0x00 ) |                                                                     |  |  |  |

|----------|------|--------------------------------|---------------------------------------------------------------------|--|--|--|

|          |      | Proximity persis               | stence. Controls rate of proximity interrupt to the host processor. |  |  |  |

|          |      | FIELD VALUE                    | INTERRUPT PERSISTENCE FUNCTION                                      |  |  |  |

|          |      | 0000                           | Every proximity cycle generates an interrupt                        |  |  |  |

| PPERS    | 7:4  | 0001                           | 1 proximity value out of range                                      |  |  |  |

|          |      | 0010                           | 2 consecutive proximity values out of range                         |  |  |  |

|          |      |                                |                                                                     |  |  |  |

|          |      | 1111                           | 15 consecutive proximity values out of range                        |  |  |  |

| Reserved | 3:0  | Reserved. Write                | e as 0.                                                             |  |  |  |

#### 6.5.7 Configuration Register (0x0D)

The configuration register sets the proximity LED drive level and wait long time.

|        | 7 | 6 | 5    | 4     | 3 | 2 | 1     | 0   | -               |

|--------|---|---|------|-------|---|---|-------|-----|-----------------|

| CONFIG |   |   | Rese | erved |   |   | WLONG | PDL | Default<br>0x00 |

| FIELD    | BITS                                                                                                                     | DESCRIPTION ( Default = 0x00 )                                                         |

|----------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Reserved | 7:2                                                                                                                      | Reserved. Write as 0.                                                                  |

| WLONG    | G 1 Wait Long. When asserted, the wait cycles are increased by a factor 12 × from that programmed in the WTIME register. |                                                                                        |

| PDL      | 0                                                                                                                        | Proximity drive level. When asserted, the proximity LDR drive current is reduced by 10 |

#### *— Sense and Actuate the world*

#### 6.5.8 Proximity Pulse Count Register (0x0E)

The proximity pulse count register sets the number of proximity pulses that the LDR pin will generate during the Prox Accum state.

| FIELD  | BITS | DESCRIPTION ( Default = 0x00 )                                                  |

|--------|------|---------------------------------------------------------------------------------|

| PPULSE | 7:0  | Proximity Pulse Count. Specifies the number of proximity pulses to be generated |

#### 6.5.9 Control Register (0x0F)

The configuration register sets the proximity LED drive level and wait long time.

|         | 7   | 6    | 5    | 4    | 3  | 2   | 1    | 0    |                 |

|---------|-----|------|------|------|----|-----|------|------|-----------------|

| CONTROL | PDR | RIVE | Rese | rved | PG | AIN | Rese | rved | Default<br>0x00 |

| FIELD    | BITS | DESCRIPT        | DESCRIPTION ( Default = 0x00 ) |            |  |  |  |  |  |

|----------|------|-----------------|--------------------------------|------------|--|--|--|--|--|

|          |      | Proximity LED [ | Proximity LED Drive Strength.  |            |  |  |  |  |  |

|          |      | FIELD VALUE     | PDL = 0                        | PDL = 1    |  |  |  |  |  |

| PDRIVE   | 7:6  | 00              | 125mA                          | 12.5mA     |  |  |  |  |  |

| PDRIVE   | 7.0  | 01              | 100mA                          | 10mA       |  |  |  |  |  |

|          |      | 10              | 75mA                           | 7.5mA      |  |  |  |  |  |

|          |      | 11              | 50mA                           | 5.0mA      |  |  |  |  |  |

| Reserved | 5:4  | Reserved. Write | e as 0.                        |            |  |  |  |  |  |

|          |      | Proximity Gain. |                                |            |  |  |  |  |  |

|          |      | FIELD VALUE     | PROXIMITY                      | GAIN VAULE |  |  |  |  |  |

| PGAIN    | 3:2  | 00              | 1X Gain                        |            |  |  |  |  |  |

| PGAIN    | 5.2  | 01              | 2X Gain                        |            |  |  |  |  |  |

|          |      | 10              | 4X Gain                        |            |  |  |  |  |  |

|          |      | 11              | 8X Gain                        |            |  |  |  |  |  |

| Reserved | 1:0  | Reserved. Write | e as 0.                        |            |  |  |  |  |  |

*— Sense and Actuate the world*

#### 6.5.10 Pulse Width Register (0x10)

The pulse width register sets the width of proximity pulses that the LDR pin will generate during the Prox Accum state.

|        | 7 | 6    | 5    | 4 | 3 | 2   | 1   | 0 |                 |

|--------|---|------|------|---|---|-----|-----|---|-----------------|

| PWIDTH |   | Rese | rved |   |   | PWI | DTH |   | Default<br>0x00 |

| FIELD    | BITS | DESCRIPT        | DESCRIPTION ( Default = 0x00 ) |  |  |  |  |

|----------|------|-----------------|--------------------------------|--|--|--|--|

| Reserved | 7:4  | Reserved. Write | Reserved. Write as 0.          |  |  |  |  |

|          |      | Proximity Width | n. 17.4us x (2 ^ PWIDTH)       |  |  |  |  |

|          |      | FIELD VALUE     | PROXIMITY PERIOD TIME          |  |  |  |  |

|          |      | 0000            | 17.4 us                        |  |  |  |  |

| PWIDH    | 3:0  | 0001            | 34.8 us                        |  |  |  |  |

|          | 5.0  | 0010            | 69.6 us                        |  |  |  |  |

|          |      |                 |                                |  |  |  |  |

|          |      | 1000            | 4454.4 us                      |  |  |  |  |

|          |      | Reserved        | Reserved                       |  |  |  |  |

#### 6.5.11 ID Register (0x12)

The ID Register provides the value for the part number. The ID register is a read-only register.

| FIELD | BITS | DESCRIPTION ( Default = 0x03 )             |

|-------|------|--------------------------------------------|

| ID    | 7:0  | Part number identification : 0x03 = SO6103 |

#### 6.5.12 STATUS Register (0x13)

The Status Register provides the internal status of the device. This register is read only.

|        | 7        | 6 | 5    | 4        | 3 | 2 | 1      | 0        |                 |

|--------|----------|---|------|----------|---|---|--------|----------|-----------------|

| STATUS | Reserved |   | PINT | Reserved |   |   | PVALID | Reserved | Default<br>0x00 |

|        |          |   |      |          |   |   |        |          |                 |

| FIELD    | BITS | DESCRIPTION ( Default = 0x00 )                                                                                       |  |

|----------|------|----------------------------------------------------------------------------------------------------------------------|--|

| Reserved | 7:6  | Reserved. Read as 0.                                                                                                 |  |

| PINT     | 1    | Proximity Interrupt. Indicates that the device is asserting a proximity interrupt.                                   |  |

| Reserved | 4:3  | Reserved. Read as 0.                                                                                                 |  |

| PVALID   | 1    | Proximity Valid. Indicates that the proximity channel has completed an integration cycle after PEN has been asserted |  |

| Reserved | 0    | Reserved. Read as 0.                                                                                                 |  |

#### 6.5.13 Proximity Data Registers (0x18 – 0x19)

Proximity data is stored as a 16-bit value. The simplest way to read both bytes is to perform a two-byte I2C read operation using the auto-increment protocol, which is set in the ADDR register TYPE field.

| REGISTER | ADDRESS | BITS | DESCRIPTION              |

|----------|---------|------|--------------------------|

| PDATAL   | 0x18    | 7:0  | Proximity data low byte  |

| PDATAH   | 0x19    | 7:0  | Proximity data high byte |

### 6.5.14 Interrupt clear Register (0xE5)

Interrupts are cleared by writing 0x00 to the Interrupt clear Register(0xE5).

Ex) I2C\_WriteByte(0x72, 0xE5, 0x00); // interrupt clear

# 7. Application

# 7.1 Typical Application

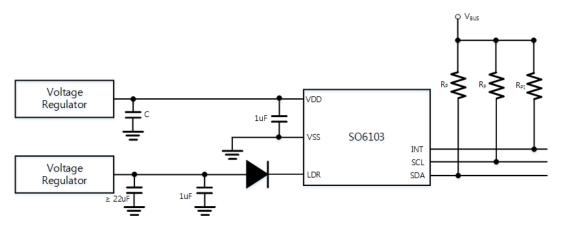

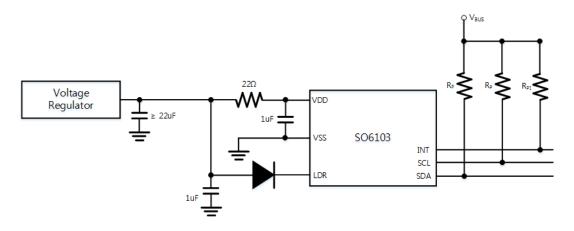

In a proximity sensing system, the IR LED can be pulsed by the SO6103 with more than 125 mA of rapidly switching current, therefore, a few design considerations must be kept in mind to get the best performance. The key goal is to reduce the power supply noise coupled back into the device during the LED pulse.

If it is not possible to provide two separate power supplies, the device can be operated from a single supply. A  $22\Omega$  resistor in series with the VDD supply line and a 1-uF low ESR capacitor effectively filter any power supply noise. The previous capacitor placement considerations apply.

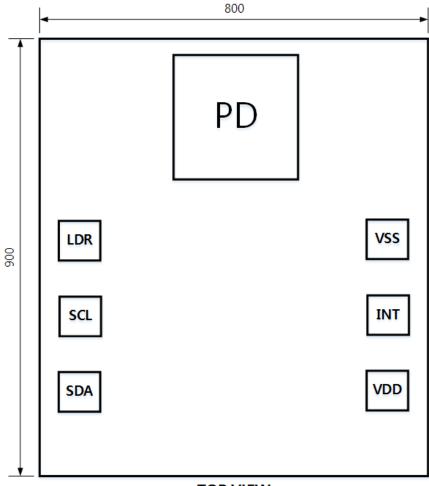

# 8. IC Dimension

- Chip Size : 800um x 900um

- PD Size : 220um x 220um

- PAD Open Size : 80um x 80um

- Scribe lane : 80um

# TOP VIEW

### To Customers:

If any product described in this document corresponds to goods or technologies which are restricted to export under the Korea "Foreign Exchange and Foreign Trade Control Law" or other applicable laws of a government having jurisdiction, then, appropriate permission for exporting such products or technologies are required to be taken.

In relation to use of the information contained in this document, no license is granted to you with regard to any intellectual property rights of SNA Co. Ltd. (hereinafter referred to as "SNA") or any third party. SNA will not be liable in any way for any claim related to infringement of intellectual property rights or other rights of third parties arising from the use of the information contained in this document.

The information concerning the circuits and other related information contained in this document is provided for referential purpose only to explain the operation or application of the products, and it will be your sole responsibility to use such information for designing of your own devices. SNA will not be liable in any way for any loss or damages incurred to you or any other party arising from the use of such information.

In general, failures in semiconductor products occur at certain percentage. Therefore, upon designing your own devices, please give due consideration to the redundancy, safety of your devices and methods to prevent occurrence of malfunction in order to avoid personal injuries, accidents or other social damages which might happen as the result of a failure of semiconductor products used in your devices.

For application of SNA products to medical equipment or other purposes where high reliability of the device is required, please contact SNA sales representative.

The contents of these documents may be subject to change without any notice, due to improvement of reliability or design of the products. It is inhibited to reproduce or copy the whole or part of this document without the permission of SNA.

SNA Co. Ltd.

*— Sense and Actuate the world*

www.sna-ic.com =